After reading this post, see https://zinka.wordpress.com/2020/05/11/my-verilog-workflow-updated/

I just started learning Verilog and FPGA design and trying to come up with a workflow that can enhance my overall learning process. I am using this blog post to record this flow which may be helpful for others as well.

In general, I do not use closed-source/proprietary software. However, it seems FPGA development using completely opensource tools may not be possible at this moment! So, I decided to use a combination of open and closed source tools (albeit all of them are free as in free beer) to start my work.

By the way, if you have just started learning FPGA design like me, DON’T MISS Dan Gisselquist‘s ZipCPU blog, probably THE BEST online resource for learning Verilog!

Editor/IDE (Sublime Text)

Choosing an editor/IDE is important for any programming. This is especially true for Verilog programming as the built-in editors that come with Vivado or Quartus are almost useless. That is the reason why these tools allow the user to choose his/her external preferred editor. Over the years, I have tried many editors to see which suits my needs better. Eclipse, Geany, Sublime Text, Atom, VSCode, to name a few. Finally, I have decided to go with Sublime Text mainly because of the following reasons:

- first and foremost, Sublime is a very lightweight application

- using packages/plugins, Sublime can be configured as an IDE for almost any language you can think of

FSM Design Tool (Fizzim)

Whether you are designing an MCU based embedded system or an FPGA based digital system, partitioning the design using FSM methodology is a must. For embedded systems, I prefer to use tools such as SMC+QFSM and Ragel. Similarly, for digital systems, Fizzim is a good FSM design tool. As I said, I am a newbie as far as Verilog coding is concerned. So, I tried to use Fizzim to design a simple UART controller to understand it’s abilities. What I have noticed is, Fizzim is a translator for your thought process. It not only helps you visualize the problem but also in visualizing the code that is going to be generated. You know exactly how your output will look like during the “drawing” stage itself. By the way, Fizzim’s tutorial is a very good place for understanding FSM concepts (don’t miss the references section). Below is a screenshot of a UART controller that I designed using fizzim.

And code generated by fizzim can be found here. I have customized ‘fizzim.pl‘ to format the code for my liking.

Workflow

- Install the following tools (I am using Lubuntu 18.04):

- Fizzim (you need JRE for running the downloaded .jar file)

- Verilator

- g++ (might have come pre-installed with your OS)

- SymbiYosys

- Install the following sublime packages for linting purposes

- Create/open a project in Sublime Text (use this Github repo as a template to start with)

- Configure fizzim.sh file and press ctrl+shift+b (and select fizzim build) to generate Verilog code from Fizzim file, txuart2.fzm. This should generate/update txuart2.v file in the rtl folder.

- Change TOPMOD in rtl/Makefile file

- Exclude .cpp files which are not required in bench/cpp/CMakeLists.txt file

- Now, again press ctrl+shift+b (and select verilog build) which does the following sequentially:

- generate .cpp files in bench/cpp/lib folder using Verilator

- build testbench written in C++ using g++ (generated files are inside bench/cpp/build folder)

- run the output file (executable) generated in the bench/cpp/build folder

- If you have generated a .vcd file using your C++ testbench, then open it using GTKWave.

- All the above steps take care of simulation and verification aspects. For synthesizing, timing analysis, etc., you need a Quartus project to which you can link Verilog files that we created in the rtl folder. This Quartus project is placed inside qproj folder.

- That’s all. Now, you start improvising.

A few more Screenshots

Sublime Text with SystemVerilog package

Code generation using Fizzim

You can add “user code” to the generated Verilog file (incremental generation)

Configuring make files

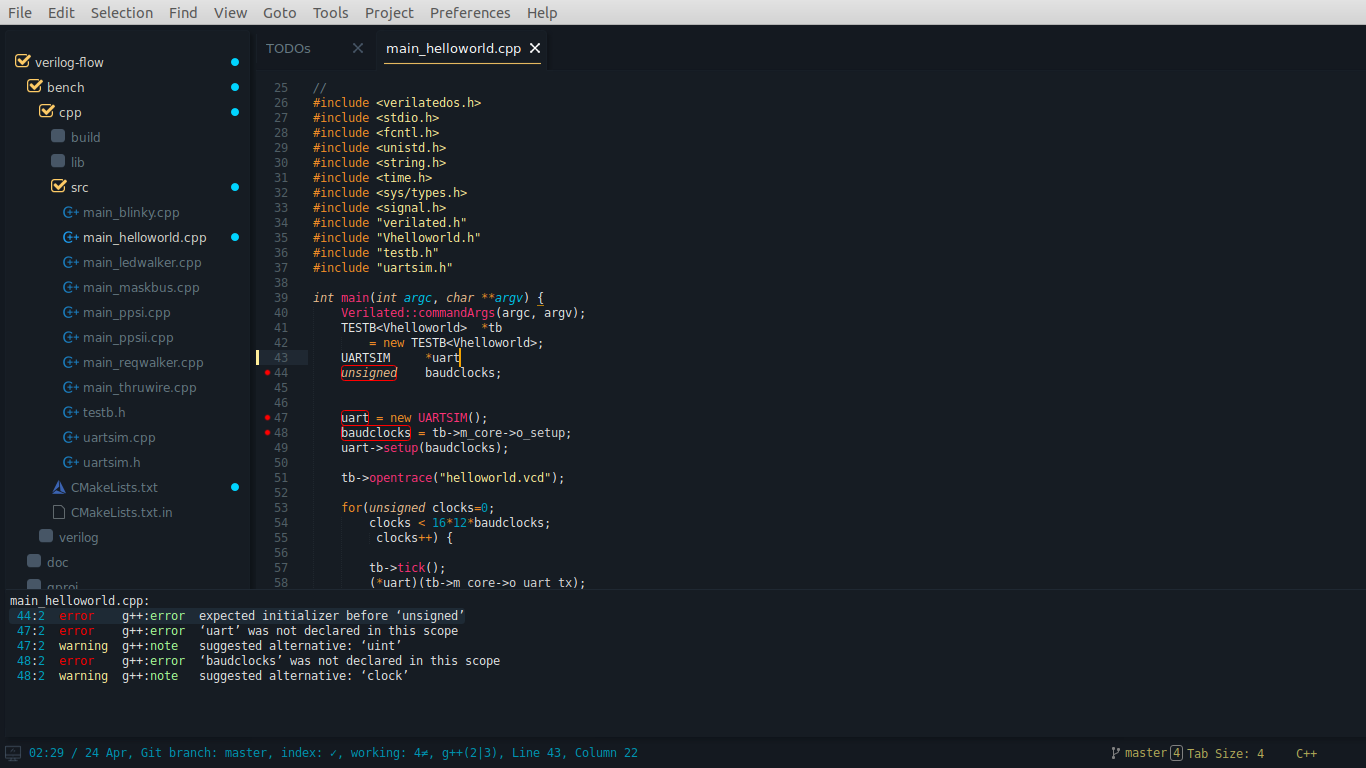

C++ linting using SublimeLinter-gcc

Viewing generated trace file in GTKWave

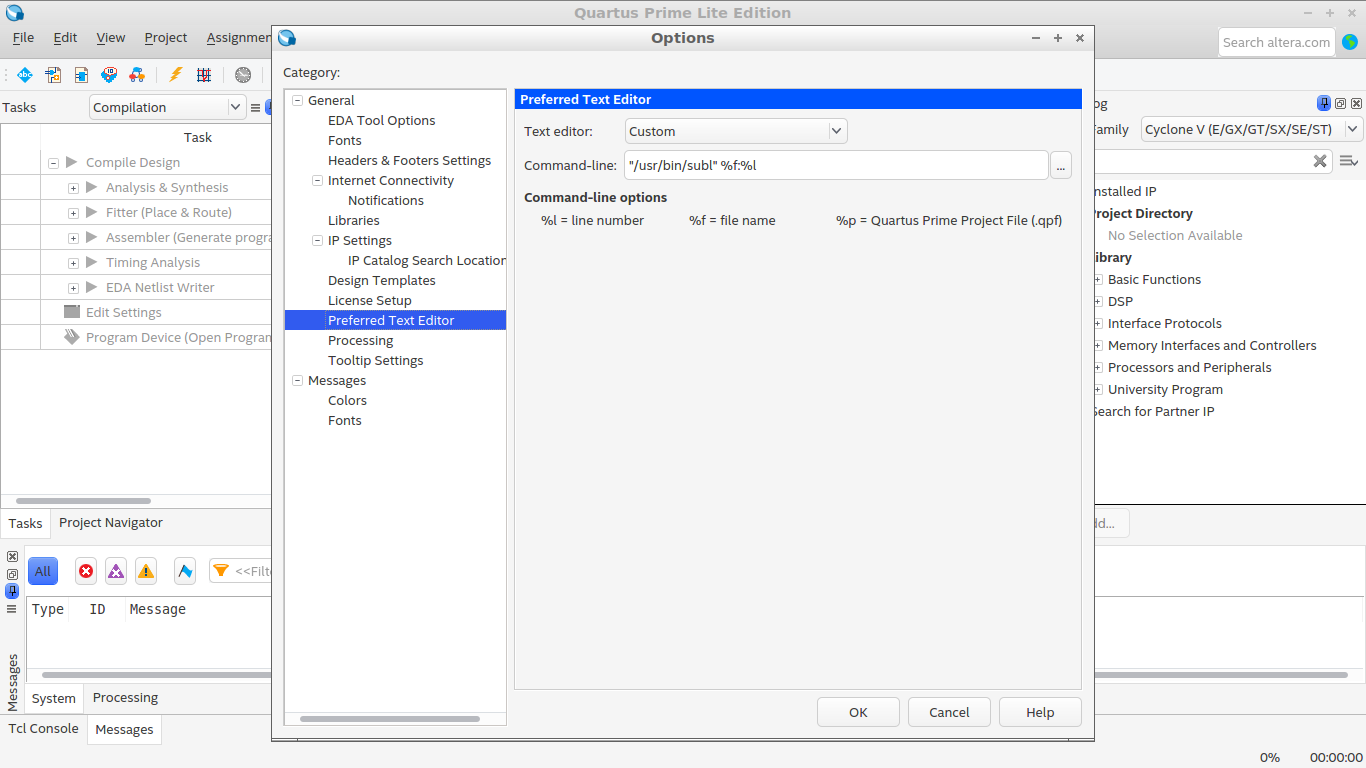

Linking Sublime Text to Quartus

List of packages that I am currently using (my user settings can be found here)